|

11/12/2022 0 Comments Period counter vhdl

Intention of this blog is educative purpose and using contents from other sites as it is fair use. In this blog, i am writing reviews about articles & books and giving free links available in world wide web. If you would like more information about this practice and to know your choices about not having this information used by these companies, click here Disclaimer Copyright of books and articles goes to its respective owners. These companies may use information (not including your name, address, email address, or telephone number) about your visits to this and other websites in order to provide advertisements about goods and services of interest to you. They uses cookies to serve ads on our site.

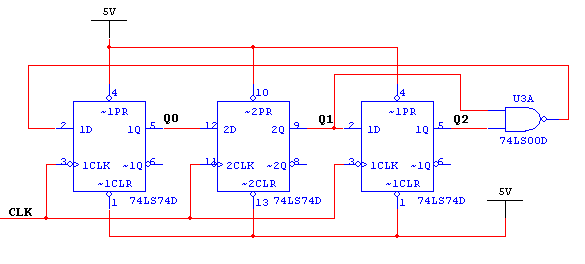

In waveform, the output at the 4th flipflop toggles and outputs johnson counter.We use third-party advertising companies to serve ads when you visit our website. Testbench waveform for 4 bit Johnson Counter wait for 100 ns rst <= '1' wait for 100 ns rst <= '0' Īll About FPGA VHDL Code for 4-bit Ring Counter and Johnson Counter | 8 Stimulus process stim_proc: process begin - hold reset state for 100 ns. VHDL Code for 4 bit Ring Counter library IEEE use IEEE.STD_LOGIC_1164.ALL Īll About FPGA VHDL Code for 4-bit Ring Counter and Johnson Counter | 2Įntity Ring_counter is Port ( CLOCK : in STD_LOGIC RESET : in STD_LOGIC Q : out STD_LOGIC_VECTOR (3 downto 0)) end Ring_counter architecture Behavioral of Ring_counter is signal q_tmp: std_logic_vector(3 downto 0):= "0000" begin process(CLOCK,RESET) begin if RESET = '1' then q_tmp CLOCK, RESET => RESET, Q => Q ) - Clock process definitions CLOCK_process :process begin CLOCK clk, rst => rst, Q => Q ) - Clock process definitions clk_process :process begin clk <= '0' wait for clk_period/2 clk <= '1' wait for clk_period/2 end process so it shift bit ‘1’ to next flipflop for each clock input and repeat the sequence as shown below. Also the first flop is set to ‘1’ at the reset state.

At each clock pulse, data at each flipflop shifted to next flipflop with last output is feed back to the input of first flipflop. Ring Counter Ring Counter very similar to shift register. VHDL Code for 4-bit Ring Counter and Johnson Counter | 1

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed